This is not investment advice. The author has no position in any of the stocks mentioned. Wccftech.com has a disclosure and ethics policy.

The Taiwan Semiconductor Manufacturing Company Limited TSMC) approved $9 billion in capital expenditure yesterday, as it looks to simultaneously focus on developing both of its latest and mature semiconductor manufacturing processes. TSMC, which is the world's largest contract chip manufacturer, is currently aggressively expanding its manufacturing capacity through building new foundries in Taiwan, the United States and Japan. These are expected to manufacture using advanced and mature chip technologies, and some of the $9 billion approved by the company's board will go towards these purposes.

TSMC Will Increase Chipmaking Capacity, Build New Plants With $9 Billion Capital Expenditure Appropriation

TSMC's current semiconductor manufacturing process roadmap involves the company manufacturing its products through the leading edge 3-nanometer (nm) during the second half of next year, with trial production for this process expected to commence soon.

Right now, its leading manufacturing process is the 5nm node, which consists of several process families, with the latest one being the N4P node. This node, according to the company, is the third refinement of the 5nm process family, and it brings 22% power efficiency and 11% performance gains over the first generation N5 node or 5nm node.

The $9 billion TSMC's board approved capital expenditure in a meeting held on Monday, and the details outline that these funds will be used for:

Approved capital appropriations of approximately US$9,036.44 million (approximately NT$239,464.84 million) for purposes including: 1) Installation and upgrade of advanced technology capacity; 2) Installation of mature and specialty technology capacity; 3) Installation of advanced packaging capacity; 4) Fab construction, installation of fab facility systems, and capitalized leased assets; 5) First quarter 2022 R&D capital investments and sustaining capital expenditures.

Some of TSMC's construction projects include a 2nm chip plant in Taiwan, a 5nm plant in Arizona, United States and another 5nm facility in Taiwan. Additionally, the company has also entered into a Japanese joint venture for a 22/28 nm plant in the country through a $2 billion equity investment.

TSMC's revenue report for October 2021 reveals that year-to-date revenue grew by 17%. Image: TSMC

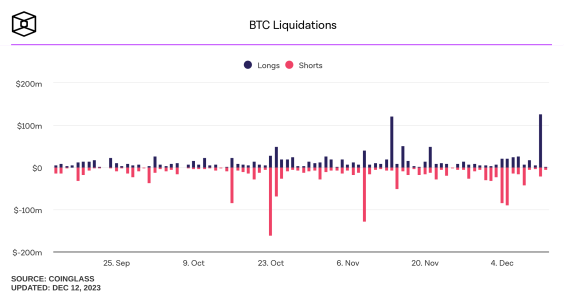

A day after its board approved the spending plans, TSMC also released its revenue report for the month of October. The details reveal that the company brought in NT$134 billion in revenue during the month, making for annual growth of roughly 13%. However, sequentially, the revenue dropped by 11.9%, falling by NT$18 billion.

In the ten months of 2021, TSMC's revenue stood at NT$1.28 trillion, as it grew by 17% over the year to date October revenue for 2020. The sequential drop comes after whispers from Taiwan have suggested that the company is due for an inventory correction as the semiconductor industry braces for a demand reduction in the wake of historic shortages and capacity growth.

These rumors, which surfaced in September, worried that TSMC's growth for the final quarter of this year could be cut in half due to order cutdowns for 5nm and 7nm smartphone modems designed to connect to fifth-generation (5G) cellular networks.

The cutdowns stand to reduce TSMC's revenue growth during the fourth quarter to 5%, and they accompanied in a debate in the financial community about TSMC' being able to grow its gross margins past 50%. In financial terminology, the gross margin refers to the ratio of a company's post direct expense revenue to its overall revenue, and a higher value reflects better cost efficiencies.

These efficiencies believe some, will stem from the 3nm node, which uses a higher amount of ultraviolet light in chip fabrication. In its N4P release, TSMC was careful to mention that the node "lowers process complexity and improves wafer cycle time by reducing the number of masks," which in turn end up reducing the direct manufacturing costs of a silicon wafer.